Microcontrollers

Never stop thinking.

#### Edition 2003-05

Published by Infineon Technologies AG, St.-Martin-Strasse 53, D-81541 München, Germany © Infineon Technologies AG 2003. All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address list).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# C868

8-Bit Single-Chip Microcontroller

### Microcontrollers

| History:   | 2003-05                             | V 1.0    |

|------------|-------------------------------------|----------|

| Version:   | -                                   |          |

| Subjects ( | (major changes since last revision) |          |

| Current da | ata updated                         |          |

| Descriptio | n of I2C included                   |          |

|            | /ersion: Subjects (                 | <b>′</b> |

#### We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

mcdocu.comments@infineon.com

## 8-Bit Single-Chip Microcontroller C800 Family

**C868**

#### **C868**

#### **Advance Information**

- C800 core :

- -Fully compatible to standard 8051 microcontroller

- -Superset of the 8051 architecture with 8 datapointers

- 40 MHz internal CPU clock

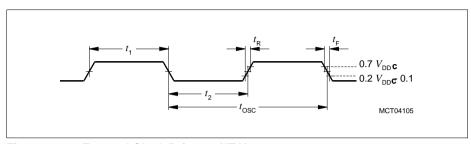

- -external clock of 6.67 10.67 MHz at 50% duty cycle

- -300 ns instruction cycle time (@37.5 MHz CPU clock)

- 8 Kbyte on-chip Program ROM for C868-1R and 8 KByte on-chip Program RAM for C868-1S

- In-system programming support for programming the XRAM(C868-1R) or XRAM/ Program RAM(C868-1S)

- -This feature is realized through 4KB Boot ROM

- 256 byte on-chip RAM

- 256 byte on-chip XRAM

(further features are on the next page)

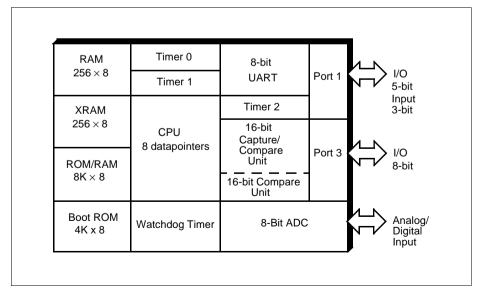

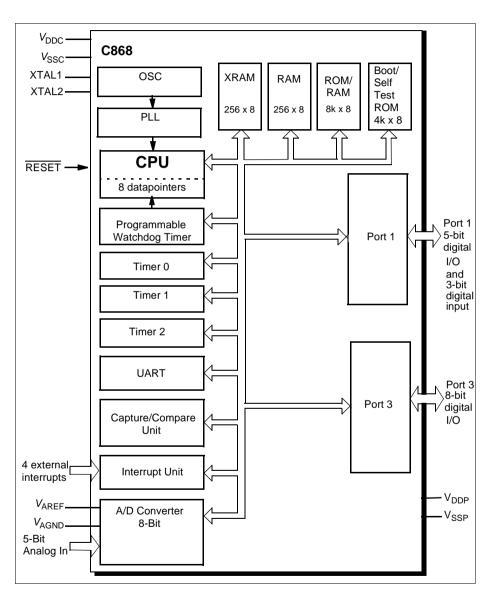

Figure 1 C868 Functional Units

- One 8-bit and one 5 bits general purpose push-pull I/O ports

- Enhanced sink current of 10 mA on Port 1/3 (total max current of 43 mA @ 100°C)

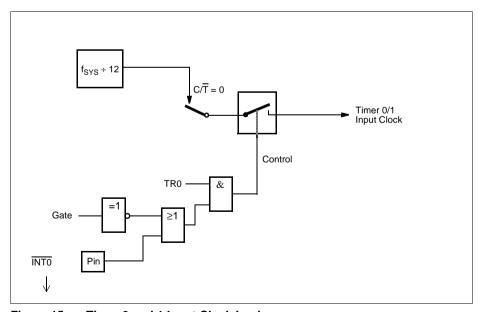

- Three 16-bit timers/counters

- -Timer 0 / 1 (C501 compatible)

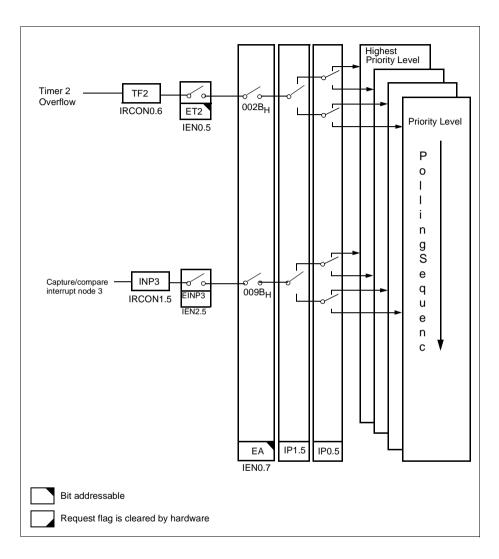

- -Timer 2 (up/down counter feature)

- -Timer 1 or 2 can be used for serial baudrate generator

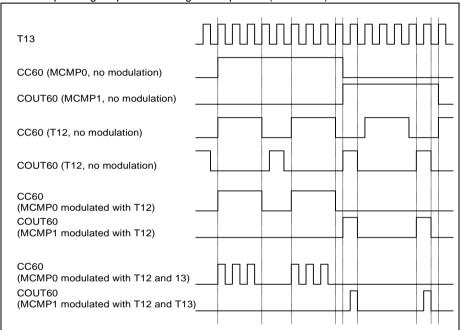

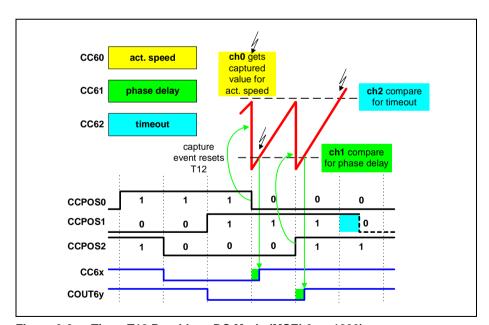

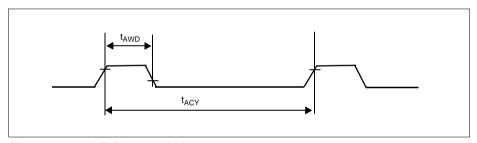

- Capture/compare unit for PWM signal generation

- -3-channel, 16-bit capture/compare unit

- -1-channel, 16-bit compare unit

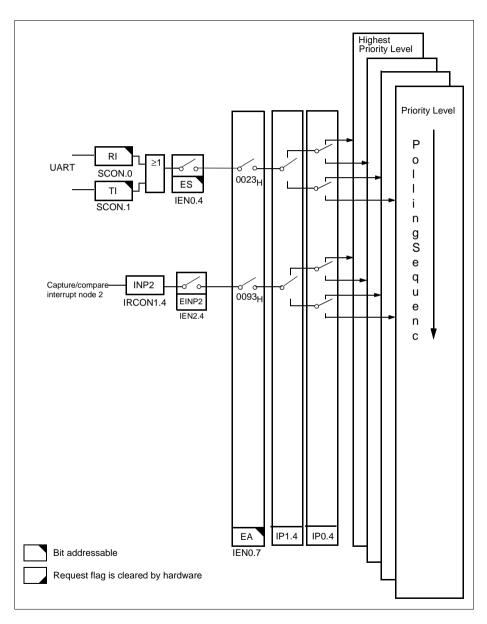

- Full duplex serial interface (UART)

- 5 channel 8-bit A/D Converter

- Start of conversion can be synchronized to capture/compare timer 12/13.

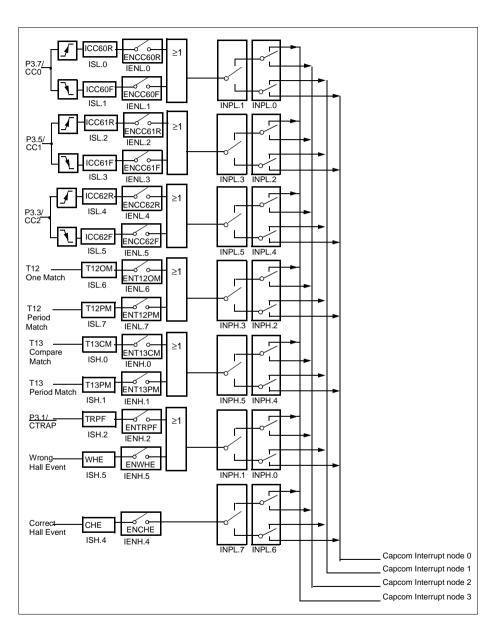

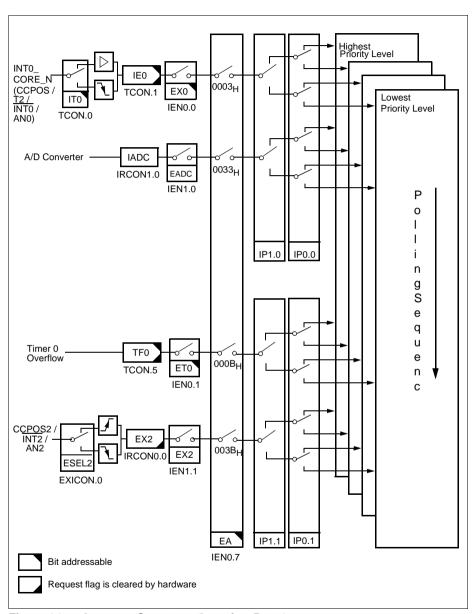

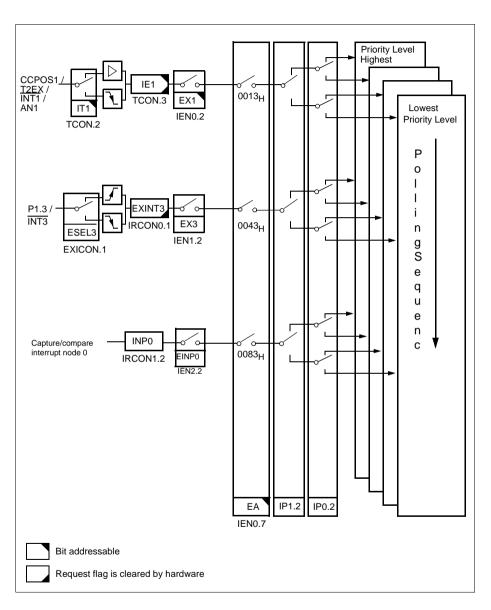

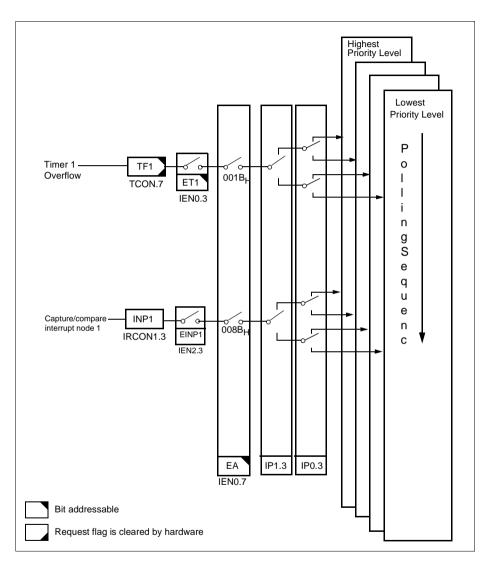

- 13 interrupt vectors with four priority levels

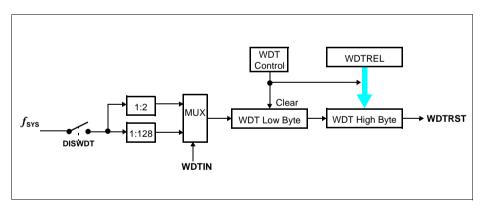

- Programmable 16-bit Watchdog Timer

- · Brown out detection

- Power Saving Modes

- -Slow-down mode

- -Idle mode (can be combined with slow-down mode)

- -Power-down mode with wake up capability through INTO or RxD pins.

BA, SAK-C868P-1SR BA, SAK-C868P-1SG BA  $T_A = -40$  to 125 °C

- Single power supply of 3.3V, internal voltage regulator for core voltage of 2.5V.

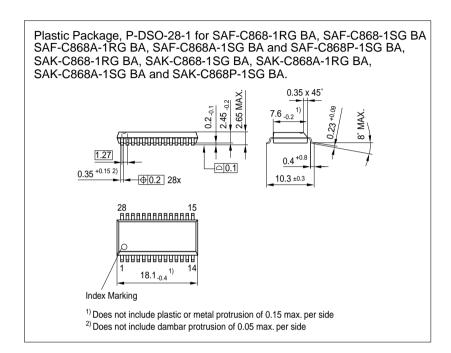

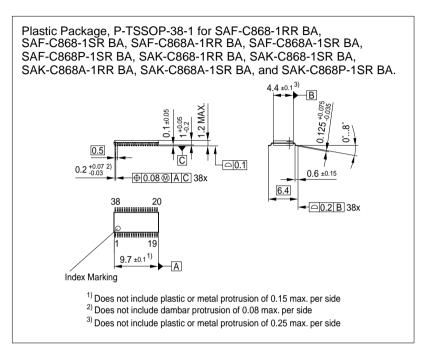

- P-DSO-28-1, P-TSSOP-38-1 packages

- · Temperature ranges:

SAF-C868-1RR BA, SAF-C868-1SR BA, SAF-C868-1RG BA, SAF-C868-1SG BA, SAF-C868A-1RR BA, SAF-C868A-1SR BA, SAF-C868A-1RG BA, SAF-C868A-1SG BA, SAF-C868P-1SR BA, SAF-C868P-1SG BA  $T_{\rm A}=-40$  to 85 °C SAK-C868-1RR BA, SAK-C868-1SR BA, SAK-C868-1RG BA, SAK-C868-1SG BA, SAK-C868A-1RR BA, SAK-C868A-1SR BA, SAK-C868A-1RG BA, SAK-C868A-1SG

Data Sheet 6 V 1.0. 2003-05

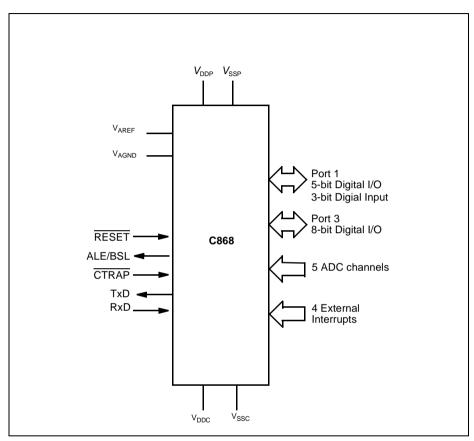

Figure 2 Logic Symbol

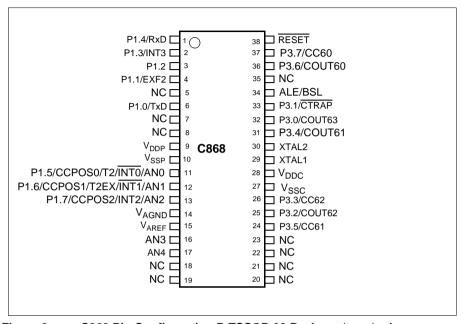

Figure 3 C868 Pin Configuration P-TSSOP-38 Package (top view)

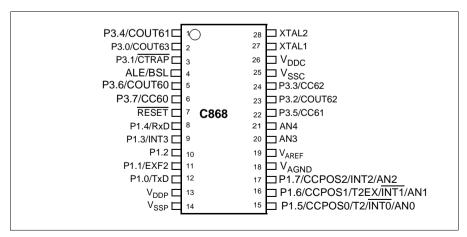

Figure 4 C868 Pin Configuration P-DSO-28 Package (top view)

Table 1 Pin Definitions and Functions

| Symbol                         | Pin Nu                   | ımbers                | I/O*)    | Function                                                                                                                                                                                                                                                                                                                          |

|--------------------------------|--------------------------|-----------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                | P-<br>DSO-<br>28         | P-<br>TSSOP-<br>38    |          |                                                                                                                                                                                                                                                                                                                                   |

| P1.0–<br>P1.4<br>P1.5-<br>P1.7 | 12-8<br>15-17            | 6,4-1                 | I/O<br>I | Port 1 is a combination of 5 bits of push-pull bidirectional I/O ports and 3 bits of input ports. As alternate digital functions, port 1 contains the interrupt 3, timer 2 overflow flag, receive data input and transmit data output of serial interface. The alternate functions are assigned to the pins of port 1 as follows: |

|                                | 12<br>11<br>10<br>9<br>8 | 6<br>4<br>3<br>2<br>1 |          | P1.0/TxD Transmit data of serial interface P1.1/EXF2 Timer 2 overflow flag P1.2 P1.3/INT3 Interrupt 3 P1.4/RxD Receive data of serial interface, Use as wakeup source from powerdown if bit WS of PMCON0 is set.                                                                                                                  |

|                                |                          |                       |          | The input ports are also interrupt ports, input to the timer2, CCU6 modules and ADC:                                                                                                                                                                                                                                              |

|                                | 15                       | 11                    | I        | P1.5/Input to Counter 2/External Interrupt 0 Input/<br>Analog Input Channel 0<br>External interrupt input or Hall input signal, counter<br>2 input or input channel 0 to the ADC unit. Use as<br>wakeup source from powerdown if bit WS of<br>PMCON0 is cleared.                                                                  |

|                                | 16                       | 12                    | I        | P1.6/Timer 2 Trigger/External Interrupt 1 Input/<br>Analog Input Channel 1<br>External interrupt input or Hall input signal, input<br>channel 1 to the ADC unit, trigger to Timer 2.                                                                                                                                              |

|                                | 17                       | 13                    | I        | P1.7/External Interrupt 2 Input/<br>Analog Input Channel 2<br>External interrupt input or Hall input signal and input<br>channel 2 to the ADC unit.                                                                                                                                                                               |

<sup>\*)</sup>I=Input O=Output

Table 1 Pin Definitions and Functions

| Symbol            | Pin Nu                                  | mbers                                        | I/O*) | Function                                                                                                                                                                                                                                                                                                                                          |  |  |

|-------------------|-----------------------------------------|----------------------------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                   | P-<br>DSO-<br>28                        | P-<br>TSSOP-<br>38                           |       |                                                                                                                                                                                                                                                                                                                                                   |  |  |

| P3.0–<br>P3.7     | 2,3,23,<br>24,1,<br>22,5,6              | 32,33,25,<br>26,31,24,<br>36,37              | I/O   | Port 3 is an 8-bit push-pull bidirectional I/O port. This port also serves as alternate functions for the CCU6 functions. The functions are assigned to the pins of port 3 as follows:                                                                                                                                                            |  |  |

|                   | 2<br>3<br>23<br>24<br>1<br>22<br>5<br>6 | 32<br>33<br>25<br>26<br>31<br>24<br>36<br>37 |       | P3.0/COUT63 16 bit compare channel output P3.1/CTRAP CCU trap input P3.2/COUT62 Output of capture/compare ch 2 P3.3/CC62 Input/output of capture/compare ch 2 P3.4/COUT61 Output of capture/compare ch 1 P3.5/CC61 Input/output of capture/compare ch 1 P3.6/COUT60 Output of capture/compare ch 0 P3.7/CC60 Input/output of capture/compare ch 0 |  |  |

| V <sub>AREF</sub> | 19                                      | 15                                           | _     | Reference voltage for the A/D converter.                                                                                                                                                                                                                                                                                                          |  |  |

| V <sub>AGND</sub> | 18                                      | 14                                           | _     | Reference ground for the A/D converter.                                                                                                                                                                                                                                                                                                           |  |  |

| AN4               | 21                                      | 17                                           | I     | Analog Input Channel 4 is input channel 4 to the ADC unit.                                                                                                                                                                                                                                                                                        |  |  |

| AN3               | 20                                      | 16                                           | I     | Analog Input Channel 3 is input channel 3 to the ADC unit.                                                                                                                                                                                                                                                                                        |  |  |

| RESET             | 7                                       | 38                                           | I     | RESET A low level on this pin for two machine cycle while the oscillator is running resets the device.                                                                                                                                                                                                                                            |  |  |

| ALE/BSL           | 4                                       | 34                                           | I/O   | Address Latch Enable/Bootstrap Mode A low level on this pin during reset allows the device to go into the bootstrap mode. After reset, this pin will output the address latch enable signal. The ALE can be disabled by bit EALE in SFR SYSCONO.                                                                                                  |  |  |

| $V_{\rm SSP}$     | 14                                      | 10                                           | _     | IO Ground (0V)                                                                                                                                                                                                                                                                                                                                    |  |  |

| $V_{DDP}$         | 13                                      | 9                                            | _     | IO Power Supply (+3.3V)                                                                                                                                                                                                                                                                                                                           |  |  |

<sup>\*)</sup>I=Input

O=Output

Table 1 Pin Definitions and Functions

| Symbol           | Pin Nu           | ımbers                             | I/O*) | Function                                                                                                                                                                                                      |  |

|------------------|------------------|------------------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                  | P-<br>DSO-<br>28 | P-<br>TSSOP-<br>38                 | -     |                                                                                                                                                                                                               |  |

| V <sub>SSC</sub> | 25               | 27                                 | _     | Core Ground (0V)                                                                                                                                                                                              |  |

| $V_{DDC}$        | 26               | 28                                 | 0     | Core Internal Reference (+2.5V) Connect 2*68 - 470nF ceramic capacitor across this pin and core ground.                                                                                                       |  |

| NC               | _                | 5,7,8,18,<br>19,20,21,<br>22,23,35 | _     | Not connected                                                                                                                                                                                                 |  |

| XTAL1            | 27               | 29                                 | I     | XTAL1 Output of the inverting oscillator amplifier.                                                                                                                                                           |  |

| XTAL2            | 28               | 30                                 | 0     | Input to the inverting oscillator amplifier and input to the internal clock generation circuits.  To drive the device from an external clock source, XTAL2 should be driven, while XTAL1 is left unconnected. |  |

<sup>\*)</sup>I=Input O=Output

Figure 5 Block Diagram of the C868

[Reset value: 00H]

#### **CPU**

The C868 is efficient both as a controller and as an arithmetic processor. It has extensive facilities for binary and BCD arithmetic and excels in its bit-handling capabilities. Efficient use of program memory results from an instruction set consisting of 44% one-byte, 41% two-byte, and 15% three-byte instructions. With a 10.67 MHz external crystal (giving a 40MHz CPU clock), 58% of the instructions execute in 300 ns.

PSW Program Status Word Register

| D7 <sub>H</sub> | D6 <sub>H</sub> | D5 <sub>H</sub> | D4 <sub>H</sub> | D3 <sub>H</sub> | D2 <sub>H</sub> | D1 <sub>H</sub> | D0 <sub>H</sub> |

|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| CY              | AC              | F0              | RS1             | RS0             | ov              | F1              | Р               |

| rwh             | rwh             | rw              | rw              | rw              | rwh             | rw              | rwh             |

| Field      | Bits | Тур | Descri                                                                                                                                        | Description                                    |                                                                |  |  |

|------------|------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|----------------------------------------------------------------|--|--|

| P          | 0    | rwh | Parity Flag Set/cleared by hardware after each instruction to indicate an odd/even number of "one" bits in the accumulator, i.e. even parity. |                                                |                                                                |  |  |

| F1         | 1    | rw  | Genera                                                                                                                                        | al Pu                                          | rpose Flag                                                     |  |  |

| ov         | 2    | rwh |                                                                                                                                               | Overflow Flag Used by arithmetic instructions. |                                                                |  |  |

| RS0<br>RS1 | 3 4  | rw  | Register Bank select control bits These bits are used to select one of the four register banks.  Table 2:                                     |                                                |                                                                |  |  |

|            |      |     | RS1                                                                                                                                           | RS0                                            | Function                                                       |  |  |

|            |      |     | 0                                                                                                                                             | 0                                              | Bank 0 selected, data address 00 <sub>H</sub> -07 <sub>H</sub> |  |  |

|            |      |     | 0                                                                                                                                             | 1                                              | Bank 1 selected, data address 08 <sub>H</sub> -0F <sub>H</sub> |  |  |

|            |      |     | 1                                                                                                                                             | 0                                              | Bank 2 selected, data address 10 <sub>H</sub> -17 <sub>H</sub> |  |  |

|            |      |     | 1                                                                                                                                             | 1                                              | Bank 3 selected, data address 18 <sub>H</sub> -1F <sub>H</sub> |  |  |

| F0         | 5    | rw  | Genera                                                                                                                                        | al Pu                                          | rpose Flag                                                     |  |  |

| AC         | 6    | rwh | Auxiliary Carry Flag Used by instructions which execute BCD operations.                                                                       |                                                |                                                                |  |  |

| CY         | 7    | rwh | _                                                                                                                                             | Carry Flag Used by arithmetic instructions.    |                                                                |  |  |

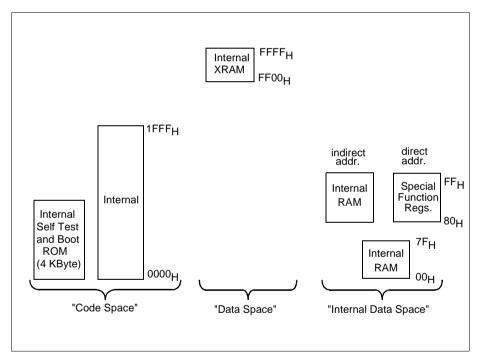

#### **Memory Organization**

The C868 CPU manipulates operands in the following five address spaces:

- up to 8 Kbyte of RAM internal program memory : 8K ROM for C868-1R

: 8K RAM for C868-1S

- 4 Kbyte of internal Self test and Boot ROM

- 256 bytes of internal data memory

- 256 bytes of internal XRAM data memory

- 128 byte special function register area

Figure 0-1 illustrates the memory address spaces of the C868.

Figure 0-1 C868 Memory Map

Data Sheet 14 V 1.0. 2003-05

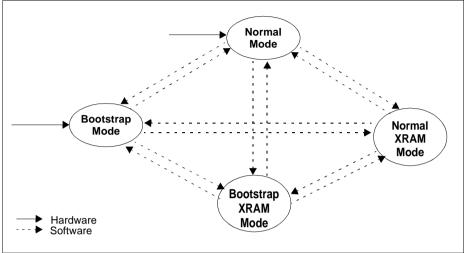

Figure 6 Entry and exit of Chip Modes

A valid hardware reset would, of course, override any of the above entry or exit procedures.

Table 0-1 Hardware and Software Selection of Chipmodes

| Operating Mode (Chipmode) | Hardware Selection                      | Software Selection                                                                     |

|---------------------------|-----------------------------------------|----------------------------------------------------------------------------------------|

| Normal Mode               | ALE/BSL pin = high<br>RESET rising edge | ALE/BSL = don't care;<br>setting bits BSLEN, SWAP = 0,0;<br>execute unlocking sequence |

| Normal XRAM Mode          | Not possible                            | setting bits BSLEN,SWAP = 0,1; execute unlocking sequence                              |

| Bootstrap XRAM Mode       | Not possible                            | setting bits BSLEN,SWAP = 1,1; execute unlocking sequence                              |

| Bootstrap Mode            | ALE/BSL pin = low<br>RESET rising edge  | ALE/BSL = don't care;<br>setting bits BSLEN, SWAP = 1,0;<br>execute unlocking sequence |

Table 3 Normal Memory Configuration

| Chip<br>Mode      | Memory Space        | Memory Boundary                                                                                  |  |  |

|-------------------|---------------------|--------------------------------------------------------------------------------------------------|--|--|

| Normal            | Code Space          | ROM/RAM: 0000 <sub>H</sub> to 1FFF <sub>H</sub>                                                  |  |  |

|                   | Internal Data Space | XRAM: FF00 <sub>H</sub> to FFFF <sub>H</sub>                                                     |  |  |

| Bootstrap         | Code Space          | Boot ROM: 0000 <sub>H</sub> to 0FFF <sub>H</sub>                                                 |  |  |

|                   | Internal Data Space | XRAM: FF00 <sub>H</sub> to FFFF <sub>H</sub><br>ROM/RAM: 0000 <sub>H</sub> to 1FFF <sub>H</sub>  |  |  |

| Normal            | Code Space          | XRAM: FF00 <sub>H</sub> to FFFF <sub>H</sub>                                                     |  |  |

| XRAM              | Data Space          | ROM/RAM: 0000 <sub>H</sub> to 1FFF <sub>H</sub>                                                  |  |  |

| Bootstrap<br>XRAM | Code Space          | Boot ROM: 0000 <sub>H</sub> to 0FFF <sub>H</sub><br>XRAM: FF00 <sub>H</sub> to FFFF <sub>H</sub> |  |  |

|                   | Data Space          | ROM/RAM: 0000 <sub>H</sub> to 1FFF <sub>H</sub>                                                  |  |  |

#### **Bootstrap loader**

The C868, includes a bootstrap mode, which is activated by setting the ALE/BSL pin at logic low with a pulldown and TxD pin at logic high with a pullup at the rising edge of the RESET. Or it can be entered by software, that is by setting BSLEN bit and resetting SWAP bit in SFR SYSCON1 accompany by an unlock sequence.

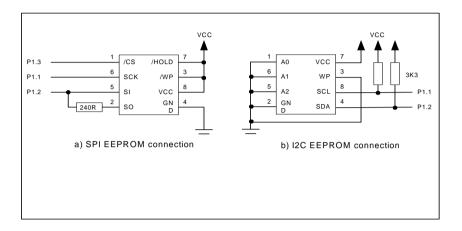

In the bootstrap mode, software routines of the bootstrap loader located in the boot ROM will be executed. Its purpose is to allow the easy and quick programming of the internal SRAM (0000 $_{\rm H}$  to 1FFF $_{\rm H}$ ) or XRAM (FF00 $_{\rm H}$  to FFFF $_{\rm H}$ ) via serial interface (UART) while the MCU is in-circuit. It also provides a way to program SRAM or XRAM through bootstrapping from an external SPI or I2C EEPROM.

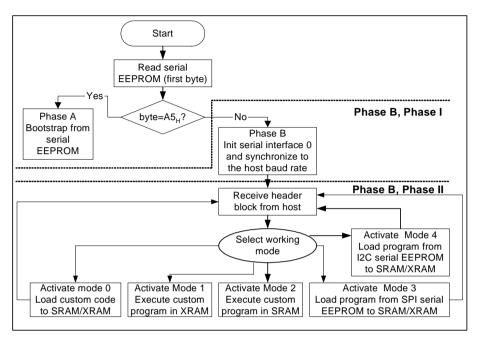

The first action of the bootstrap loader is to detect the presence of EEPROM and its type, SPI or I2C, and check the first byte of the serial EEPROM. If the first byte is  $0A5_H$ , the MCU would enter Phase A to download from the EEPROM. Otherwise, it will enter Phase B to establish a serial communication with the connected host. Bootstrapping from the serial EEPROM can also be done in phase B if it is invoked by the host.

Phase B consists of two functional parts that represent two phases:

- Phase I: Establish a serial connection and automatically synchronize to the transfer speed (baud rate) of the serial communication partner (host).

- Phase II: Perform the serial communication with the host. The host controls the communication by sending special header information, which select one of the working modes. These modes are:

Table 4 Serial Communication Modes of Phase B Modes Description 0 Transfer a customer program from the host to the SRAM (0000<sub>H</sub> to 1FFF<sub>H</sub>) or XRAM (FF00<sub>H</sub> -FFFF<sub>H</sub>). Then return to the beginning of phase II and wait for the next command from the host. Execute a customer program in the XRAM at start address FF00<sub>H</sub>. 1 2 Execute a customer program in the SRAM at start address 0000<sub>H</sub>. 3 Transfer a customer program from the SPI EEPROM to the SRAM (0000<sub>H</sub> to 1FFF<sub>H</sub>) or XRAM (FF00<sub>H</sub> -FFFF<sub>H</sub>). Then return to the beginning of phase II and wait for the next command from the host. 4 Transfer a customer program from the I2C EEPROM to the SRAM  $(0000_{H}$  to 1FFF<sub>H</sub>) or XRAM (FF00<sub>H</sub> -FFFF<sub>H</sub>). Then return to the beginning of phase II and wait for the next command from the host. 5-9 reserved

The phases of the bootstrap loader are illustrated in **Figure 7**.

Figure 7 The phases of the Bootstrap Loader

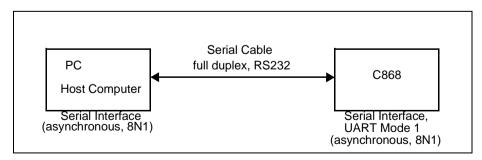

The serial communication is activated in phase B. Using a full duplex serial cable (RS232), the MCU must be connected to the serial port of the host computer as shown in **Figure 8**.

Figure 8 Bootstrap Loader Interface to the PC

Figure 9 EEPROM connections for a) SPI and b) I2C

#### **Reset and Brownout**

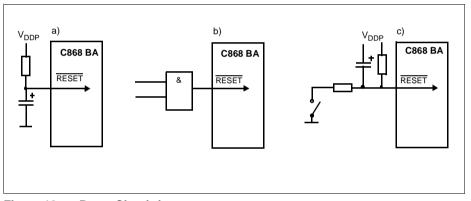

The reset input is an <u>active</u> low input. An internal Schmitt trigger is used at the input for noise rejection. The RESET pin must be held low for at least tbd usec. But the CPU will only exit from reset condition after the PLL lock had been detected.

During  $\overline{\text{RESET}}$  at transition from low to high, C868 will go into normal mode if ALE/BSL is high and bootstrap loading mode if ALE/BSL is low. A pullup to  $V_{DDP}$  or pulldown to ground is recommended for pin ALE/BSL. TXD should have a pullup to  $V_{DDP}$  and should not be stimulated externally during reset, as a logic low at this pin will cause the chip to go into test mode if ALE/BSL is low.

Figure 10 shows the possible reset circuits, note that the RESET pin does not have an internal pullup resistance.

Figure 10 Reset Circuitries

An on-chip analog circuit detects brownout, if the core voltage  $V_{DDC}$  dips below the threshold voltage  $V_{THRESHOLD}$  momentarily while  $\overline{RESET}$  pin is high. If this detection is active for tbd usec then the device will reset. When  $V_{DDC}$  recovers by exceeding  $V_{THRESHOLD}$  while  $\overline{RESET}$  is high, the reset is released once PLL is locked for 4096 clocks. Bit BO in the PMCON0 register is set when brownout detected if brownout detection was enabled, this bit is cleared by hardware reset  $\overline{RESET}$  and software. All ports are tristated during brownout.

The  $V_{THRESHOLD}$  has a nominal value of 1.47V, a minimum value of 1.1V and a maximum value of 1.8V.

Data Sheet 20 V 1.0. 2003-05

#### **Clock system**

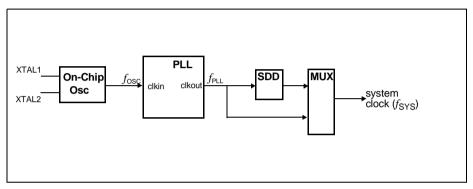

The C868 clock system consist of the on-chip oscillator, PLL and multiplexer stage. The programmable Slow Down Divider (SDD) divides the PLL output clock frequency by a factor of 1...32 which is specified via CMCON.REL. The system clock is switched from the PLL output to the output from the SDD when slowdown mode is selected.

Figure 11 Block Diagram of the Clock Generation

The PLL output frequency is determined by:

$$f_{\text{PLL}} = f_{\text{VCO}} / \text{K} = \frac{15}{\text{K}} \times f_{\text{OSC}}$$

[1]

The range for the VCO frequency is given by:

$$100 \text{ MHz} \le f_{\text{VCO}} \le 160 \text{ MHz}$$

[2]

The relationship between the input frequency and VCO frequency is given by:

$$f_{\text{VCO}} = 15 \times f_{\text{OSC}}$$

[3]

This gives the range for the input frequency which is given by:

$$6.67 \text{ MHz} \le f_{OSC} \le 10.67 \text{ MHz}$$

[4]

Table 5 Output Frequencies  $f_{PLL}$  Derived from Various Output Factors

| K-Factor           |                  | f <sub>P</sub>             | LL                         | Duty      | Jitter                                                                  |

|--------------------|------------------|----------------------------|----------------------------|-----------|-------------------------------------------------------------------------|

| Selected<br>Factor | KDIV             | f <sub>VCO</sub> = 100 MHz | f <sub>VCO</sub> = 160 MHz | Cycle [%] |                                                                         |

| 2                  | 000 <sub>B</sub> | 50                         | 80                         | 50        | linear depending on f <sub>VCO</sub>                                    |

| 4                  | 010 <sub>B</sub> | 25                         | 40                         | 50        | at f <sub>VCO</sub> =100MHz: +/-300ps                                   |

| 5 <sup>1)</sup>    | 011 <sub>B</sub> | 20                         | 32                         | 40        | at f <sub>VCO</sub> =160MHz: +/-250ps<br>additional jitter for odd Kdiv |

| 6                  | 100 <sub>B</sub> | 16.67                      | 26.67                      | 50        | factors tbd.                                                            |

| 8                  | 101 <sub>B</sub> | 12.5                       | 20                         | 50        |                                                                         |

| 9 <sup>1)</sup>    | 110 <sub>B</sub> | 11.11                      | 17.78                      | 44        |                                                                         |

| 10                 | 111 <sub>B</sub> | 10                         | 16                         | 50        |                                                                         |

| 16                 | 001 <sub>B</sub> | 6.25                       | 10                         | 50        |                                                                         |

These odd factors should not be used (not tested because off the unsymmetrical duty cycle).

<sup>2)</sup> Shaded combinations should not be used because they are above the maximum CPU frequency of 40MHz.

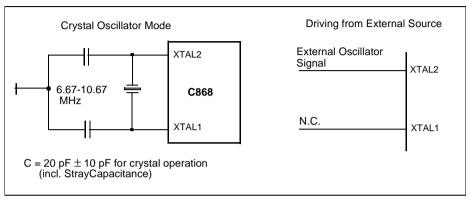

Figure 12 shows the recommended oscillator circuitries for crystal and external clock operation.

Figure 12 Recommended Oscillator Circuit

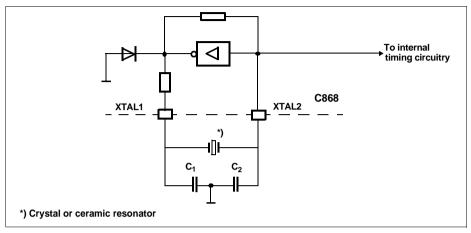

In this application the on-chip oscillator is used as a crystal-controlled, positive-reactance oscillator (a more detailed schematic is given in **Figure 13**). It is operated in its fundamental response mode as an inductive reactor in parallel resonance with a capacitor external to the chip. The crystal specifications and capacitances are non-critical. In this circuit tbd pF can be used as single capacitance at any frequency together with a good quality crystal. A ceramic resonator can be used in place of the crystal in cost-critical applications. If a ceramic resonator is used, the two capacitors normally have different values depending on the oscillator frequency. We recommend consulting the manufacturer of the ceramic resonator for value specifications of these capacitors.

Data Sheet 23 V 1.0, 2003-05

Figure 13 On-Chip Oscillator Circuitry

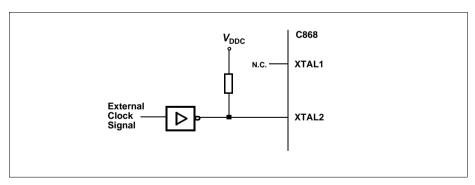

To drive the C868 with an external clock source, the external clock signal has to be applied to XTAL2, as shown in **Figure 14**. XTAL1 has to be left unconnected. A pullup resistor is suggested (to increase the noise margin), but is optional if  $V_{\rm OH}$  of the driving gate corresponds to the  $V_{\rm IH2}$  specification of XTAL2.

Figure 14 External Clock Source

Data Sheet 24 V 1.0, 2003-05

[Reset value: XX10XXX1<sub>B</sub>]

#### 0.1 Special Function Registers

All registers, except the program counter and the four general purpose register banks, reside in the special function register area. The special function register area consists of two portions: the standard special function register area and the mapped special function register area. For accessing the mapped special function area, bit RMAP in special function register SYSCON0 must be set. All other special function registers are located in the standard special function register area which is accessed when RMAP is cleared ("0").

### SYSCON0 System Control Register 0

| 7 | 6 | 5    | 4    | 3 | 2 | 1 | 0     |

|---|---|------|------|---|---|---|-------|

| - | - | EALE | RMAP | - | - | - | XMAP0 |

| r | r | rw   | rw   | r | r | r | rw    |

#### The functions of the shaded bits are not described here

| Field | Bits  | Тур | Description                                                                                                                                                                                                      |

|-------|-------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RMAP  | 4     | rw  | Special Function Register Map Control RMAP = 0: The access to the non-mapped (standard) special function register area is enabled. RMAP = 1: The access to the mapped special function register area is enabled. |

| -     | [7:2] | r   | reserved;<br>returns '0' if read; should be written with '0';                                                                                                                                                    |

As long as bit RMAP is set, the mapped special function register area can be accessed. This bit is not cleared automatically by hardware. Thus, when non-mapped/mapped registers are to be accessed, the bit RMAP must be cleared/set respectively by software.

The 109 special function registers (SFR) include pointers and registers that provide an interface between the CPU and the other on-chip peripherals. All available SFRs whose address bits 0-2 are 0 (e.g.  $80_H$ ,  $88_H$ ,  $90_H$ , ...,  $F0_H$ ,  $F8_H$ ) are bit- addressable. Totally there are 128 directly addressable bits within the SFR area.

All SFRs are listed in **Table 6** and **Table 7**.In **Table 6** they are organized in groups which refer to the functional blocks of the C868-1R, C868-1S. **Table 7** illustrates the contents (bits) of the SFRs

Table 6 **Special Function Registers - Functional Blocks**

| Block       | Symbol                                                                                                       | Name                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Add-<br>ress                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Contents<br>after<br>Reset                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C800 core   | ACC B DPH DPL DPSEL PSW SP SCON SBUF IEN0 IEN1 IEN2 IP0 IP1 TCON TMOD TL0 TL1 TH0                            | Accumulator B-Register Data Pointer, High Byte Data Pointer, Low Byte Data Pointer Select Register Program Status Word Register Stack Pointer Serial Channel Control Register Serial Data Buffer Interrupt Enable Register 0 Interrupt Enable Register 1 Interrupt Enable Register 2 Interrupt Priority Register 0 interrupt Priority Register 1 Timer 0/1 Control Register Timer Mode Register Timer 0, Low Byte Timer 1, Low Byte Timer 0, High Byte | E0 <sub>H</sub> <sup>1</sup> 83 <sub>H</sub> 82 <sub>H</sub> 84 <sub>H</sub> D0 <sub>H</sub> <sup>1</sup> 83 <sub>H</sub> 82 <sub>H</sub> 84 <sub>H</sub> 99 <sub>H</sub> A3 <sub>H</sub> B3 <sub>H</sub> A3 <sub>H</sub> | 00H<br>00H<br>00H<br>00H<br>00H<br>00H<br>00H<br>00H                                                                                                                                                                                                                                                                                                                                                               |

|             | TH1<br>PCON                                                                                                  | Timer 1, High Byte Power Control Register                                                                                                                                                                                                                                                                                                                                                                                                              | 8D <sub>H</sub><br>87 <sub>H</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 00 <sub>H</sub><br>0XXX0000 <sub>B</sub> <sup>2)</sup>                                                                                                                                                                                                                                                                                                                                                             |

| Sys-<br>tem | PMCON0<br>CMCON<br>EXICON<br>IRCON0<br>IRCON1<br>PMCON1<br>PMCON2<br>SCUWDT<br>VERSION<br>SYSCON0<br>SYSCON1 | Wake-up Control Register Clock Control Register External Interrupt Control Register External Interrupt Request Register Peripheral Interrupt Request Register Peripheral Management Ctrl Register Peripheral Management Status Register Peripheral Management Status Register SCU/Watchdog Control Register ROM Version Register System Control Register 0 System Control Register 1                                                                   | 8E <sub>H</sub><br>8F <sub>H</sub><br>91 <sub>H</sub><br>92 <sub>H</sub><br>93 <sub>H</sub><br><b>E8<sub>H</sub></b> <sup>1)</sup><br><b>C0<sub>H</sub></b> <sup>1)</sup><br>F9 <sub>H</sub><br>AD <sub>H</sub><br>AF <sub>H</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | XXX00000 <sub>B</sub> <sup>2)</sup> 10011111 <sub>B</sub> XXXXXX00 <sub>B</sub> <sup>2)</sup> XXXXXX000 <sub>B</sub> <sup>2)</sup> X0X00000 <sub>B</sub> <sup>2)</sup> 00 <sub>H</sub> XX10XXX1 <sub>B</sub> <sup>2)</sup> 00XXX0X0 <sub>B</sub> <sup>2)</sup> |

Bit-addressable special function registers

"X" means that the value is undefined and the location is reserved

<sup>3)</sup> Register is mapped by bit RMAP in SYSCON0.4=1

<sup>4)</sup> Register is mapped by bit RMAP in SYSCON0.4=0

Table 6 Special Function Registers - Functional Blocks (cont'd)

| Block                  | Symbol                                                                                | Name                                                                                                                                                      | Add-<br>ress                                                                                                                 | Contents<br>after<br>Reset                                                                                                        |

|------------------------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| A/D-<br>Con-<br>verter | ADCON0<br>ADCON1<br>ADDATH                                                            | A/D Converter Control Register 0 A/D Converter Control Register 1 A/D Converter Data Register                                                             | D8 <sub>H</sub> <sup>1)</sup><br>D9 <sub>H</sub><br>DB <sub>H</sub>                                                          | <b>00<sub>H</sub></b><br>XX000000 <sub>B</sub> <sup>2)</sup><br>00 <sub>H</sub>                                                   |

| Ports                  | P1 <sup>4)</sup> P1DIR <sup>3)</sup> P3 <sup>4)</sup> P3DIR <sup>3)</sup> P3ALT P1ALT | Port 1 Register Port 1 Direction Register Port 3 Register Port 3 Direction Register Port 3 Alternate Function Register Port 1 Alternate Function Register | 90H <sup>1)</sup><br>90H <sup>1)</sup><br>B0H <sup>1)</sup><br>B0H <sup>1)</sup><br>B1H<br>B4H                               |                                                                                                                                   |

| Watch<br>dog           | WDTCON<br>WDTREL<br>WDTL<br>WDTH                                                      | Watchdog Timer Control Register<br>Watchdog Timer Reload Register<br>Watchdog Timer, Low Byte<br>Watchdog Timer, High Byte                                | A2 <sub>H</sub><br>A3 <sub>H</sub><br>B2 <sub>H</sub><br>B3 <sub>H</sub>                                                     | XXXXXX00 <sub>B</sub> <sup>2)</sup><br>00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub>                                      |

| Timer<br>2             | T2CON<br>T2MOD<br>RC2H<br>RC2L<br>T2H<br>T2L                                          | Timer 2 Control Register Timer 2 Mode Register Timer 2 Reload/Capture, High Byte Timer 2 Reload/Capture, Low Byte Timer 2, High Byte Timer 2, Low Byte    | C8 <sub>H</sub> <sup>1)</sup><br>C9 <sub>H</sub><br>CB <sub>H</sub><br>CA <sub>H</sub><br>CD <sub>H</sub><br>CC <sub>H</sub> | 00 <sub>H</sub><br>XXXXXXX0 <sub>B<sup>2)</sup><br/>00<sub>H</sub><br/>00<sub>H</sub><br/>00<sub>H</sub><br/>00<sub>H</sub></sub> |

<sup>1)</sup> Bit-addressable special function registers

<sup>2) &</sup>quot;X" means that the value is undefined and the location is reserved

<sup>3)</sup> Register is mapped by bit RMAP in SYSCON0.4=1

<sup>4)</sup> Register is mapped by bit RMAP in SYSCON0.4=0

Table 6 Special Function Registers - Functional Blocks (cont'd)

| Block | Symbol               | Name                                    | Add-<br>ress    | Contents<br>after<br>Reset |

|-------|----------------------|-----------------------------------------|-----------------|----------------------------|

| Cap-  | T12L                 | Timer T12 Counter Register, Low Byte    | ECH             | 00 <sub>H</sub>            |

| ture/ | T12H                 | Timer T12 Counter Register, High Byte   | $ED_H$          | 00 <sub>H</sub>            |

| Com-  | T13L                 | Timer T13 Counter Register, Low Byte    | EEH             | 00 <sub>H</sub>            |

| pare  | T13H                 | Timer T13 Counter Register, High Byte   | $EF_H$          | 00 <sub>H</sub>            |

| Unit  | T12PRL               | Timer T12 Period Register, Low Byte     | $DE_H$          | 00 <sub>H</sub>            |

|       | T12PRH               | Timer T12 Period Register, High Byte    | $DF_H$          | 00 <sub>H</sub>            |

|       | T13PRL               | Timer T13 Period Register, Low Byte     | D2 <sub>H</sub> | 00 <sub>H</sub>            |

|       | T13PRH               | Timer T13 Period Register, High Byte    | D3 <sub>H</sub> | 00 <sub>H</sub>            |

|       | CC60RL               | Capture/Compare Ch 0 Reg, Low Byte      | C2 <sub>H</sub> | 00 <sub>H</sub>            |

|       | CC60RH               | Capture/Compare Ch 0 Reg, High Byte     | C3 <sub>H</sub> | 00 <sub>H</sub>            |

|       | CC61RL               | Capture/Compare Ch 1 Reg, Low Byte      | C4 <sub>H</sub> | 00 <sub>H</sub>            |

|       | CC61RH               | Capture/Compare Ch 1 Reg, High Byte     | C5 <sub>H</sub> | 00 <sub>H</sub>            |

|       | CC62RL               | Capture/Compare Ch 2 Reg, Low Byte      | C6 <sub>H</sub> | 00 <sub>H</sub>            |

|       | CC62RH               | Capture/Compare Ch 2 Reg, High Byte     | C7 <sub>H</sub> | 00 <sub>H</sub>            |

|       | CC63RL               | T13 Compare Register, Low Byte          | D4 <sub>H</sub> | 00 <sub>H</sub>            |

|       | CC63RH               | T13 Compare Register, High Byte         | D5 <sub>H</sub> | 00 <sub>H</sub>            |

|       | T12DTCL              | Timer T12 Dead Time Ctrl, Low Byte      | E6 <sub>H</sub> | 00 <sub>H</sub>            |

|       | T12DTCH              | Timer T12 Dead Time Ctrl, High Byte     | E7 <sub>H</sub> | 00 <sub>H</sub>            |

|       | CMPSTATL             | Compare Timer Status, Low Byte          | F4 <sub>H</sub> | 00 <sub>H</sub>            |

|       | CMPSTATH             | Compare Timer Status, High Byte         | F5 <sub>H</sub> | 00 <sub>H</sub>            |

|       | CMPMODIFL            | Compare Timer Modification, Low Byte    | $EA_H$          | 00 <sub>H</sub>            |

|       | CMPMODIFH            | Compare Timer Modification, High Byte   | $EB_H$          | 00 <sub>H</sub>            |

|       | TCTR0L               | Timer Control Register 0, Low Byte      | E2 <sub>H</sub> | 00 <sub>H</sub>            |

|       | TCTR0H               | Timer Control Register 0, High Byte     | E3 <sub>H</sub> | 00 <sub>H</sub>            |

|       | TCTR2L <sup>3)</sup> | Timer Control Register 2, Low Byte      | F2 <sub>H</sub> | 00 <sub>H</sub>            |

|       | TCTR4L4)             | Timer Control Register 4, Low Byte      | F2 <sub>H</sub> | 0 <sub>H</sub>             |

|       | TCTR4H4)             | Timer Control Register 4, High Byte     | F3 <sub>H</sub> | 00 <sub>H</sub>            |

|       | ISL                  | Cap/Com Interrupt Register, Low Byte    | E4 <sub>H</sub> | 00 <sub>H</sub>            |

|       | ISH                  | Cap/Com Interrupt Register, High Byte   | E5 <sub>H</sub> | 00 <sub>H</sub>            |

|       | PISELH               | Port Input Selector Register, High Byte | $BB_H$          | 00 <sub>H</sub>            |

<sup>1)</sup> Bit-addressable special function registers

<sup>2) &</sup>quot;X" means that the value is undefined and the location is reserved

<sup>3)</sup> Register is mapped by bit RMAP in SYSCON0.4=1

<sup>4)</sup> Register is mapped by bit RMAP in SYSCON0.4=0

Table 6 Special Function Registers - Functional Blocks (cont'd)

| Block | Symbol                 | Name                                    | Add-<br>ress    | Contents<br>after<br>Reset |

|-------|------------------------|-----------------------------------------|-----------------|----------------------------|

| Сар-  | ISSL <sup>3)</sup>     | Cap/Com Int Status Set Reg, Low Byte    | BC <sub>H</sub> | 00 <sub>H</sub>            |

| ture/ | ISSH <sup>3)</sup>     | Cap/Com Int Status Set Reg, High Byte   | $BD_H$          | 00 <sub>H</sub>            |

| Com-  | ISRL <sup>4)</sup>     | Cap/Com Int Status Reset Reg, Low Byte  | $BC_H$          | 00 <sub>H</sub>            |

| pare  | ISRH4)                 | Cap/Com Int Status Reset Reg, High Byte | $BD_H$          | 00 <sub>H</sub>            |

| Unit  | INPL <sup>3)</sup>     | Cap/Com Int Node Ptr Reg, Low Byte      | $BE_H$          | 40 <sub>H</sub>            |

|       | INPH <sup>3)</sup>     | Cap/Com Int Node Ptr Reg, High Byte     | $BF_H$          | 39 <sub>H</sub>            |

|       | IENL <sup>4)</sup>     | Cap/Com Interrupt Register, Low Byte    | $BE_H$          | 00 <sub>H</sub>            |

|       | IENH4)                 | Cap/Com Interrupt Register, High Byte   | $BF_H$          | 00 <sub>H</sub>            |

|       | CC60SRL                | Cap/Com Channel 0 Shadow, Low Byte      | $FA_H$          | 00 <sub>H</sub>            |

|       | CC60SRH                | Cap/Com Channel 0 Shadow, High Byte     | $FB_H$          | 00 <sub>H</sub>            |

|       | CC61SRL                | Cap/Com Channel 1 Shadow, Low Byte      | $FC_H$          | 00 <sub>H</sub>            |

|       | CC61SRH                | Cap/Com Channel 1 Shadow, High Byte     | $FD_H$          | 00 <sub>H</sub>            |

|       | CC62SRL                | Cap/Com Channel 2 Shadow, Low Byte      | FE <sub>H</sub> | 00 <sub>H</sub>            |

|       | CC62SRH                | Cap/Com Channel 2 Shadow, High Byte     | $FF_H$          | 00 <sub>H</sub>            |

|       | CC63SRL                | T13 Compare Shadow Reg, Low Byte        | B6 <sub>H</sub> | 00 <sub>H</sub>            |

|       | CC63SRH                | T13 Compare Shadow Reg, High Byte       | B7 <sub>H</sub> | 00 <sub>H</sub>            |

|       | MODCTRL <sup>3)</sup>  | Modulation Control Register, Low Byte   | D6 <sub>H</sub> | 00 <sub>H</sub>            |

|       | MODCTRH3)              | Modulation Control Register, High Byte  | D7 <sub>H</sub> | 00 <sub>H</sub>            |

|       | TRPCTRL                | Trap Control Register, Low Byte         | CEH             | 00 <sub>H</sub>            |

|       | TRPCTRH                | Trap Control Register, High Byte        | CF <sub>H</sub> | 00 <sub>H</sub>            |

|       | PSLRL                  | Passive State Level Register, Low Byte  | A6 <sub>H</sub> | 00 <sub>H</sub>            |

|       | MCMOUTL <sup>3)</sup>  | MCM Output Register, Low Byte           | $DC_H$          | 00 <sub>H</sub>            |

|       | MCMOUTH <sup>3)</sup>  | MCM Output Register, High Byte          | $DD_H$          | 00 <sub>H</sub>            |

|       | MCMOUTSL4)             | MCM Output Shadow Register, Low Byte    | $DC_H$          | 00 <sub>H</sub>            |

|       | MCMOUTSH4)             | MCM Output Shadow Register, High Byte   | $DD_H$          | 00 <sub>H</sub>            |

|       | MCMCTRLL <sup>4)</sup> | MCM Control Register, Low Byte          | D6 <sub>H</sub> | 00 <sub>H</sub>            |

|       | T12MSELL               | T12 Cap/Com Mode Sel Reg, Low Byte      | F6 <sub>H</sub> | 00 <sub>H</sub>            |

|       | T12MSELH               | T12 Cap/Com Mode Sel Reg, High Byte     | F7 <sub>H</sub> | 00 <sub>H</sub>            |

<sup>1)</sup> Bit-addressable special function registers

<sup>2) &</sup>quot;X" means that the value is undefined and the location is reserved 3) Register is mapped by bit RMAP in SYSCON0.4=1

<sup>4)</sup> Register is mapped by bit RMAP in SYSCON0.4=0

Table 7 Contents of the SFRs, SFRs in numeric order of their addresses

| Addr                         | Reg-<br>ister | Content<br>after<br>Reset <sup>1)</sup> | Bit 7     | Bit 6 | Bit 5 | Bit 4 | Bit 3     | Bit 2      | Bit 1      | Bit 0      |

|------------------------------|---------------|-----------------------------------------|-----------|-------|-------|-------|-----------|------------|------------|------------|

| 81 <sub>H</sub>              | SP            | 07 <sub>H</sub>                         | .7        | .6    | .5    | .4    | .3        | .2         | .1         | .0         |

| 82 <sub>H</sub>              | DPL           | 00 <sub>H</sub>                         | .7        | .6    | .5    | .4    | .3        | .2         | .1         | .0         |

| 83 <sub>H</sub>              | DPH           | 00 <sub>H</sub>                         | .7        | .6    | .5    | .4    | .3        | .2         | .1         | .0         |

| 84 <sub>H</sub>              | DPSE<br>L     | 00 <sub>H</sub>                         | _         | _     | _     | _     | _         | D2         | D1         | D0         |

| 87 <sub>H</sub>              | PCON          | 0XX0<br>0000 <sub>B</sub>               | SMOD      | _     | _     | SD    | GF1       | GF0        | PDE        | IDLE       |

| 88 <sub>H</sub>              | TCON          | 00 <sub>H</sub>                         | TF1       | TR1   | TF0   | TR0   | IE1       | IT1        | IE0        | IT0        |

| 89 <sub>H</sub>              | TMOD          | 00 <sub>H</sub>                         | GATE<br>1 | C/NT1 | M1(1) | M0(1) | GATE<br>0 | C/NT0      | M1(0)      | M0(0)      |

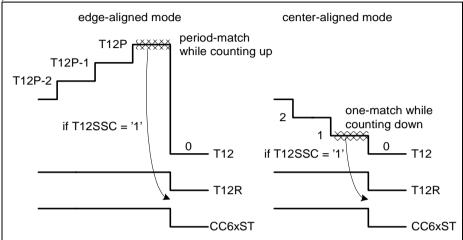

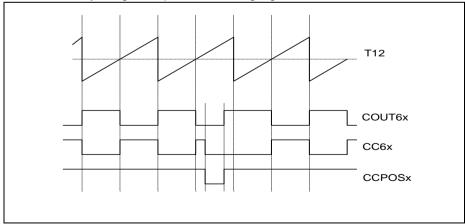

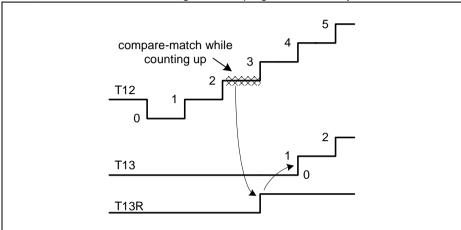

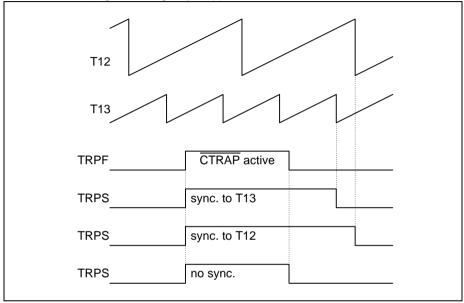

| 8A <sub>H</sub>              | TL0           | 00 <sub>H</sub>                         | .7        | .6    | .5    | .4    | .3        | .2         | .1         | .0         |